# EGC442 Class Notes 5/2/2023

**Baback Izadi** Division of Engineering Programs bai@engr.newpaltz.edu

### Required design documentation for the Project

**1. Register file:** With appropriate detail, show the layout of the register file.

**2. ALU:** You need to show a detailed design of an ALU to support the following instructions: Table 4: Instruction set for required design

- **1. Data Path:** Show the data path of each class of instruction as well as the overall data path per Table 4.

- **a.** Control: Develop the control logic to support your instructions. Gate level design in not necessary.

- However, functional table needs be very detailed and clear, making it implementable in an FPGA.

2. Pipelined Data Path: Show the data path for the pipelined architecture.

## Extra Credits (20 Points):

Note: Extra Points are only considered if the processor design is over 80% correct.

Either Verilog code or a schematic capture of the ALU is needed. Documentation should include two simulation cases for each ALU operation.

| Score /Max                         |        | Instruction | Operation                      | ALU function |

|------------------------------------|--------|-------------|--------------------------------|--------------|

|                                    | Point  | LDUR        | load register                  | add          |

| Register File                      | 9/10   | CTUD        |                                | - 11         |

| ALU Design                         | 13/15  | STUR        | store register                 | add          |

| Data Path                          | 27/30  | CBZ         | Conditional branch on zero     | pass input b |

| Control                            | 15/15  | CD) 17      |                                |              |

| Pipelined Data Path                | 14/15  | CBNZ        | Conditional branch on not zero | pass input b |

| English                            | 14/15  | В           | Unconditional branch           |              |

| TurnItIn similarity negative score | 0      | В           | Unconditional branch           |              |

| Total                              | 92/100 | R-type      | add                            | add          |

| Extra Credits                      | /20    | it type     |                                |              |

| Total Course Project               | 92/100 |             | subtract                       | subtract     |

| Applicability for Design Folder:   |        |             | AND                            | AND          |

|                                    | X Yes  |             |                                |              |

|                                    | No     |             | ORR                            | OR           |

|                                    |        |             |                                |              |

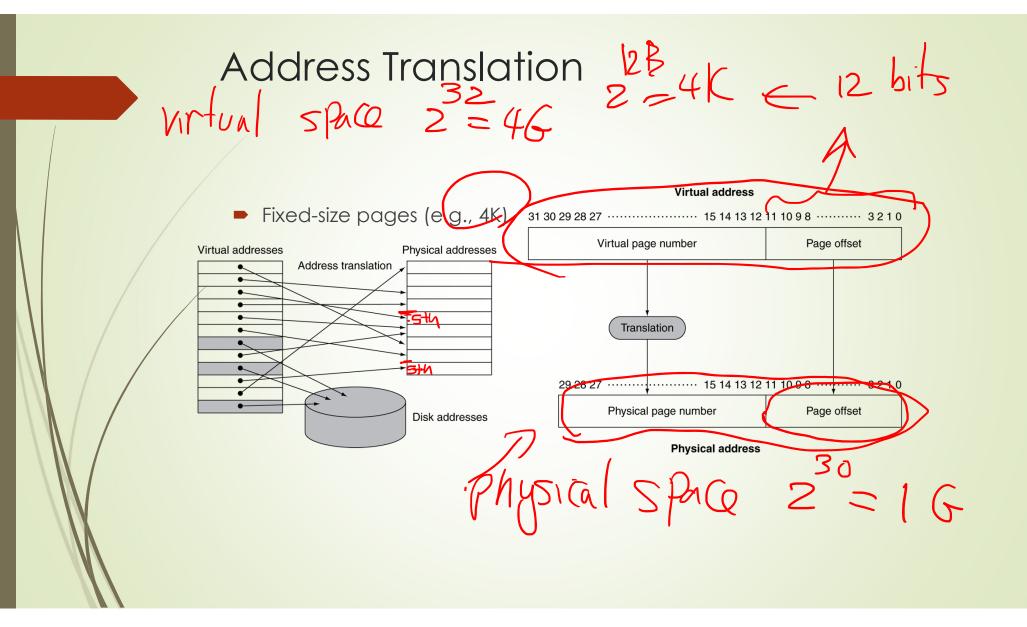

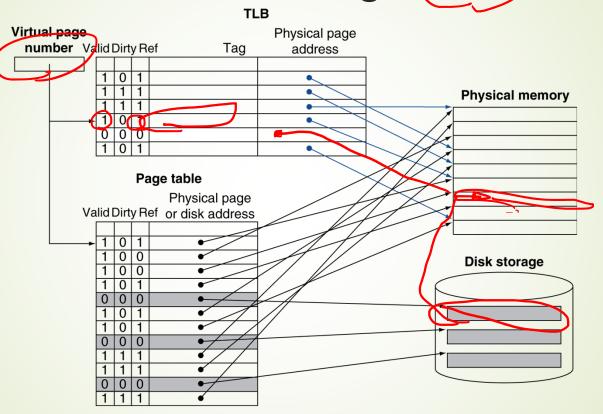

# Fast Translation Using a TLB

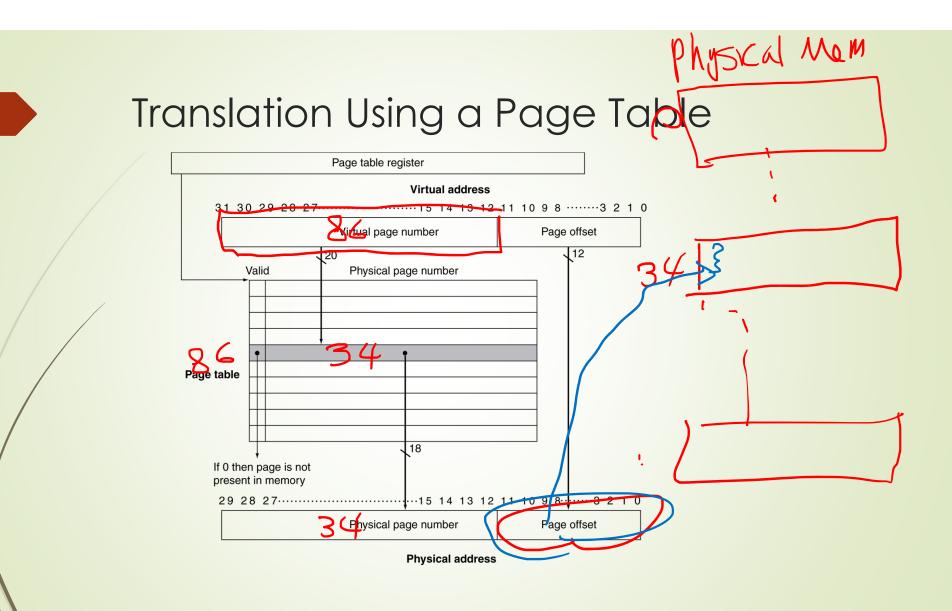

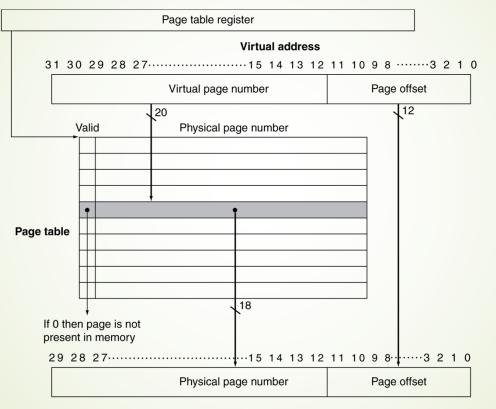

# Translation Using a Page Table

Physical address

1) A virtual machine (VM) is an emulation that provides a hardware interface.

O True

- False

- A system VM allows a computer to share hardware resources amongst multiple operating systems.

🖲 True

O False

When a computer runs multiple VMs, the first VM launched is called the host, and the other VMs are called the guests.

O True

- False

- 4) Another name for a VMM is a hypervisor.

🖲 True

O False

5) A VMM is the same size as the corresponding OS.

O True

- 🖲 False

- A VMM should not allow a guest VM to change how resources are allocated.

- 🖲 True

- O False

$\overline{Z}$ ) A VMM runs in system mode, while a guest VM runs in user mode.

- True

- O False

#### Correct

A virtual machine is an emulation that provides a *software* interface.

#### Correct

If a computer is running copies of many different operating systems (OSes) using VMs, each OS needs to use the hardware resources.

#### Correct

The computer hardware running the VMs is the host, and the VMs are the guests.

#### Correct

The VMM (virtual machine monitor) or hypervisor is the software the supports virtual machines. The VMM determines how to map the VMs' virtual resources to physical hardware resources.

#### Correct

The VMM is a reduced version of a full OS.

#### Correct

A VMM should also run a guest VM as if the VM is on the native hardware.

#### Correct

The VMM must have a higher privilege level than a guest VM. System mode provides a more privileged set of instructions that can be used to control all system resources.

| Protection      | Mechanisms that prevent multiple processes that use the same hardware from interfering with each other.                                                         | Corre |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|                 | One such mechanism is the translation of a program's address space to a physical address accessible only to this program.                                       |       |

| Virtual memory  | A technique where main memory is used as a cache for secondary storage.                                                                                         | Corre |

|                 | Virtual memory is used to safely share memory amongst programs and remove the burdens related to the limited size of main memory.                               |       |

| Address mapping | The process of mapping a virtual address to a physical address.                                                                                                 | Corre |

|                 | Address mapping is also called address translation. The physical address may map to a location in main memory or disk.                                          |       |

| Virtual address | An address that corresponds to a location in virtual space.                                                                                                     | Corr  |

|                 | Address mapping assigns a virtual address to a physical address when memory is accessed. Multiple virtual addresses can be mapped to a single physical address. |       |

| Page fault      | A virtual memory miss.                                                                                                                                          | Corre |

|                 | A page fault occurs when an accessed page is not in main memory.                                                                                                |       |

| <ul> <li>In a virtual memory system, an is to is to individual word</li> <li>entire page</li> <li>entire page</li> <li>A bit indicates if a page has been with memory.</li> <li>dirty</li> <li>use</li> </ul> |                                                                                                                                                                                                              | Correct<br>Writes can take millions of processor clock cycles, so<br>copying back an entire page is more efficient than writing<br>individual words back to the disk.<br>Correct<br>A dirty bit is set when any word in a page is written and<br>indicates if a page needs to be copied back when the<br>page is replaced. Alternatively, a reference bit or use bit is<br>set when a page is accessed, regardless of whether the |         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| cache                                                                                                                                                                                                         | of recently used translations                                                                                                                                                                                | page is written to, to indicate if the page was touched<br>during a particular time period and is a good candidate<br>for replacement.                                                                                                                                                                                                                                                                                            | Correct |

|                                                                                                                                                                                                               | The TLB allows the processor to avoid accessing the page table, which is located in<br>memory.                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |

| status bits                                                                                                                                                                                                   | Each TLB entry includes the physical page address, tag, and<br>The TLB, rather than the page table, is accessed for every reference. Thus, the TLB must similarly include a valid, reference, and dirty bit. |                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |

| fewer                                                                                                                                                                                                         | A TLB has number of entries as a page table.<br>A TLB has many fewer entries than a page table, relying on locality of reference to<br>improve access performance.                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |

| write-back                                                                                                                                                                                                    |                                                                                                                                                                                                              | g a scheme.<br>need to be copied back to the page table entry when<br>e bits are the only portion of the TLB entry that can be                                                                                                                                                                                                                                                                                                    | Correct |

| The the following TLB, virtual memory system, and cache miss combinations possible or impossible?        |         |

|----------------------------------------------------------------------------------------------------------|---------|

| TLB hit, page table miss, cache miss     Correct                                                         |         |

| O Possible A TLB translation cannot occur if the page is not in                                          |         |

| Impossible     memory.                                                                                   |         |

| TLB miss, page table miss, cache hit                                                                     |         |

| O Possible Data cannot exist in a cache if the page is not in memory.                                    |         |

|                                                                                                          |         |

| TLB hit, page table hit, cache miss                                                                      |         |

| Possible                                                                                                 |         |

| O Impossible Though possible, the page table will not be checked if there is a TLB hit.                  |         |

| TLB hit, page table miss, cache hit                                                                      |         |

| O Possible                                                                                               |         |

| A TLB translation cannot occur if the page is not in memory.                                             |         |

| 13 memory.                                                                                               |         |

| A cache for a cache.                                                                                     |         |

|                                                                                                          | Correct |

| L1 cache L1 cache, known as the primary cache, can be used as a cache for the L2 cache if the L2 exists. |         |

| LZ EXISIS.                                                                                               | l       |

| A cache for main memory.                                                                                 | Correct |

| L2 cache The L2 cache is faster than main memory, but tends to be larger and slower than the L1          |         |

| cache.                                                                                                   |         |

| A cache for disks.                                                                                       | Correct |

| Main memory           The virtual memory technique uses main memory as a cache for data on disks.        |         |

|                                                                                                          | U<br>n  |

| A cache for page table entries.                                                                          | Correct |

| TLB The translation look-aside buffer stores recent address mappings to avoid page table                 |         |

| nie danosta od obie odnej od obie od obie od obie od obie od obie page dane                              |         |

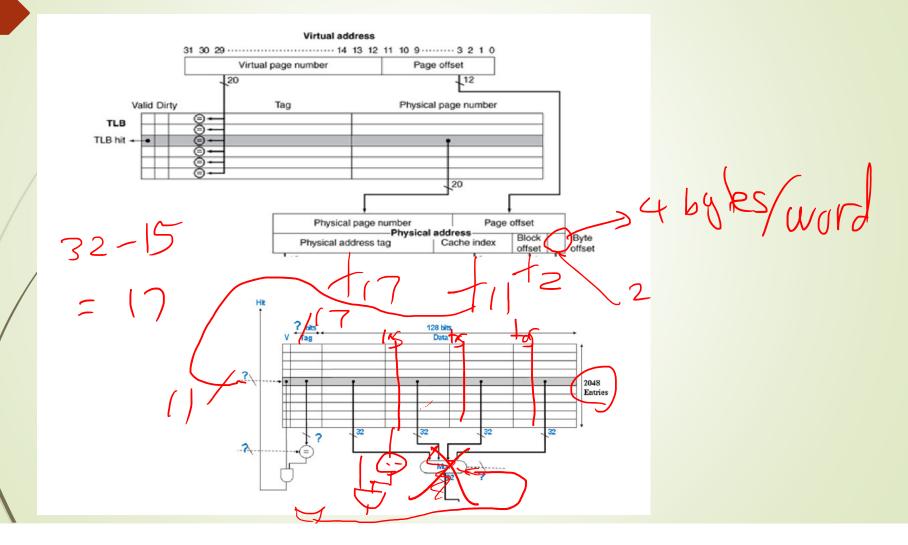

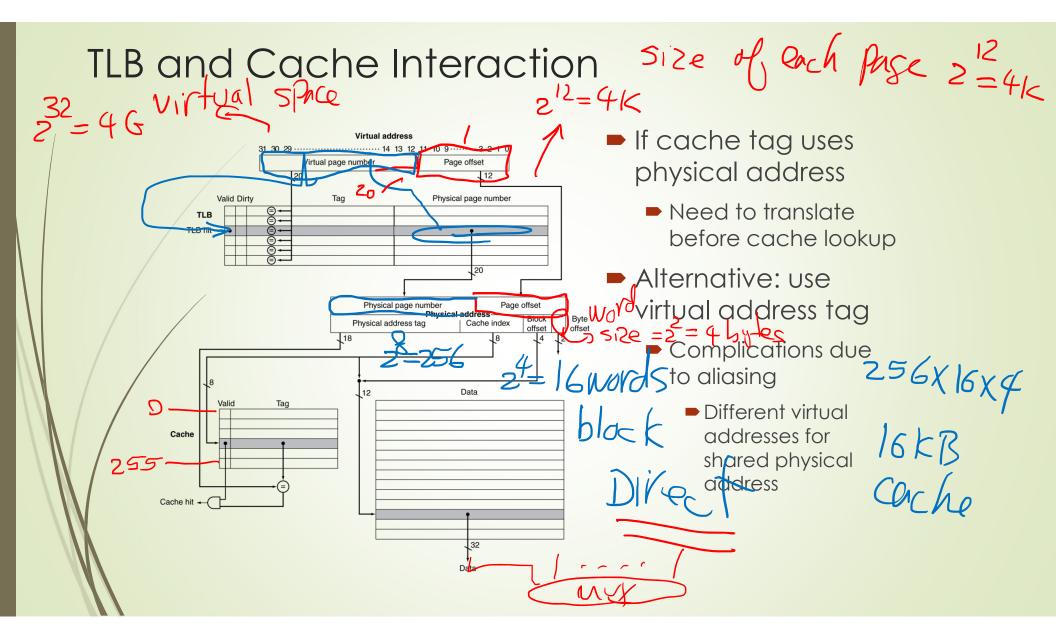

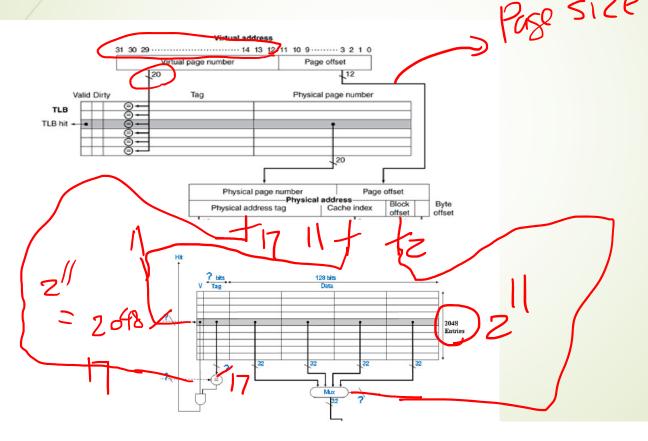

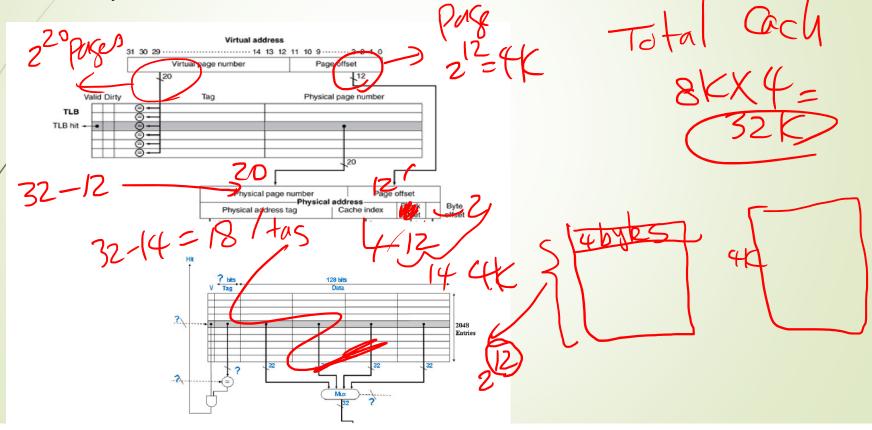

14) The figure below depicts the memory system.

- > Page SIZE = 2/2=4/C how many bits is each connection.

14) The figure below depicts the memory system.

- a. What is the function of TLB?

- b. How many virtual pages numbers does the system have and how many bytes is each page?

- c. Identify type of cache architecture

- d. Complete the cache architecture by connecting the dash lines to appropriate physical address. Identify how many bits is each connection.

- 14) The figure below depicts the memory system.

- a. Modify it for 4 way associative cache.